|

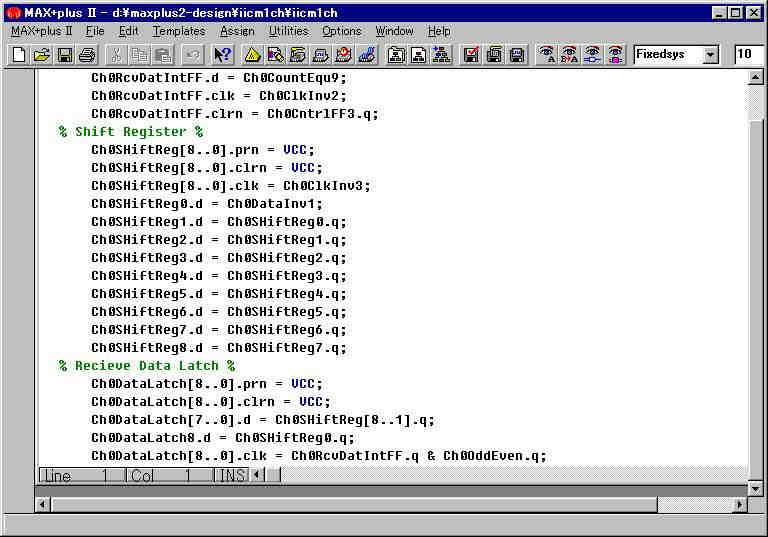

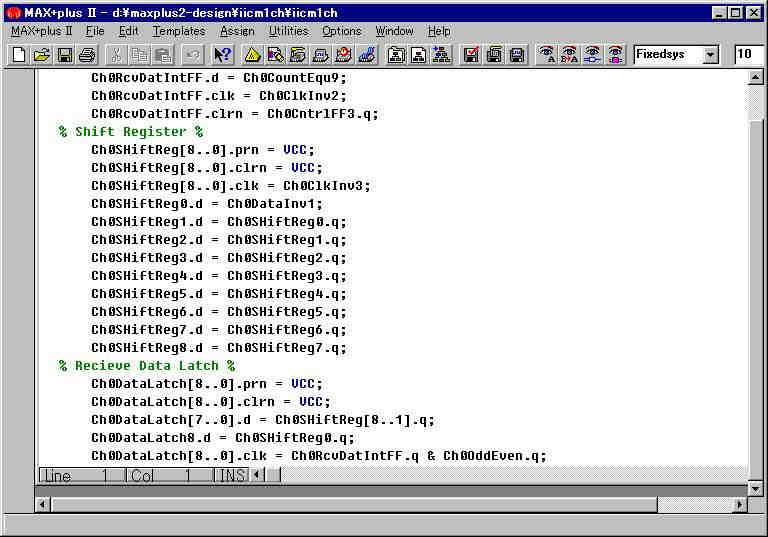

| ADHL言語で記述しているところ |

●PLDロジックの設計

『1』 開発環境とデバッグ

今回のPLDは、アルテラ社のEPM7064SLCを使用しますので、開発環境はMAX+PLUSⅡを用います。

ロジックはADHL言語・VHDL言語で作成し、デバッグはMAX+PLUSⅡのロジックシュミレーターで行います。

|

| ADHL言語で記述しているところ |

『2』 PLDの機能

IICバスのデータをクロックエッジでサンプルし、9ビット毎にシリアル→パラレル

変換をさせます。

変換後の9ビットパラレルデータを内部レジスターにラッチと同時に メインマイコンへの割り込み要求出力を

イネーブルにさせます。

また、スタートコンディション・ストップコンディション条件の監視も行い、条件の

成立時にメインマイコンへの

割り込み要求出力をイネーブルにします。